在现代高速数字系统中,时钟信号的完整性直接影响着系统的性能和稳定性。时钟缓冲器作为时钟树设计的核心组件,承担着信号分配、噪声隔离和时序优化的关键任务。随着5G通信、AI芯片和数据中心等领域的快速发展,工程师在选型与设计时钟缓冲器时,既要满足多路低抖动输出的需求,又要应对复杂电磁环境下的信号完整性问题。本文将深入剖析时钟缓冲器技术选型的核心指标与设计中的隐性风险点,为工程师提供可落地的解决方案。

一、技术选型的五大黄金准则

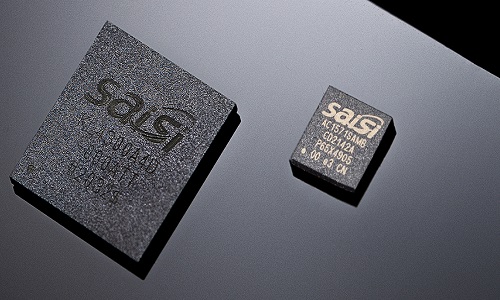

1. 抖动性能:系统时序的生死线

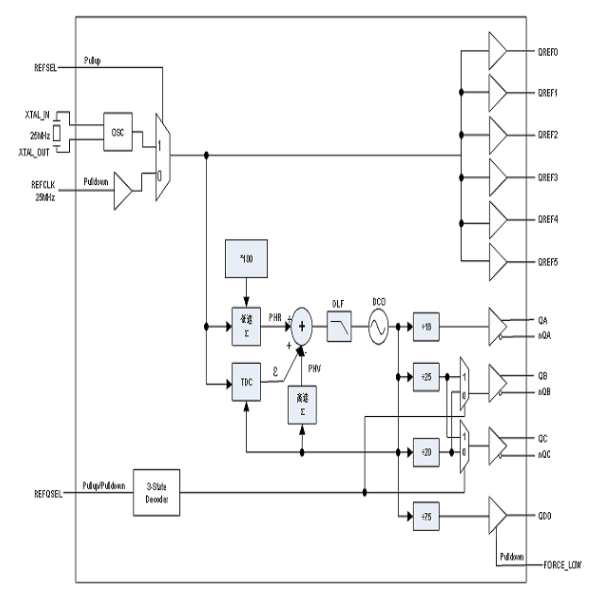

时钟缓冲器的输出抖动(Jitter)直接决定下游电路的时序余量。根据IEEE 1156标准,RMS相位抖动应低于300fs@156.25MHz才能满足高速SerDes接口要求。例如,赛思的AC系列通过混合信号PLL架构,在1.8V供电下实现<100fs的超低抖动,特别适用于400G光模块等场景。

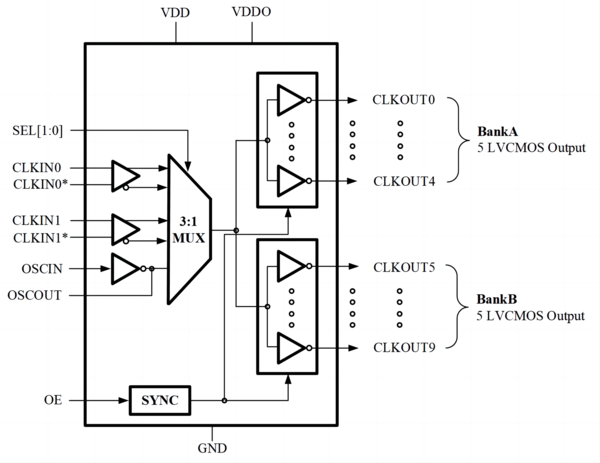

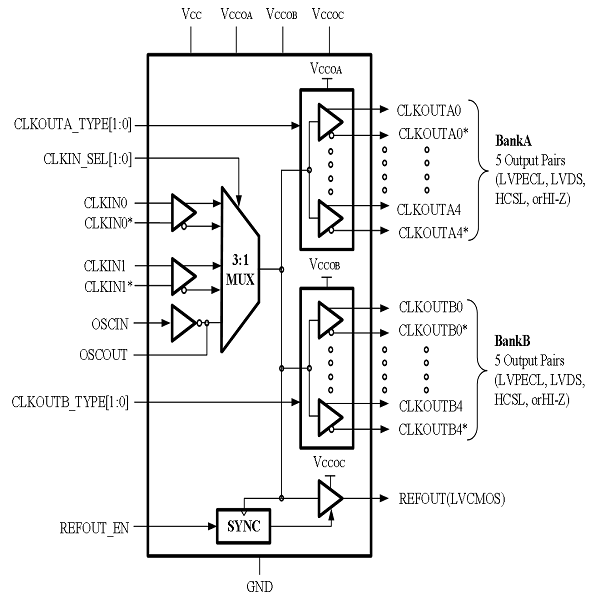

2. 输出通道数与灵活性

在多核处理器和FPGA系统中,时钟缓冲器的输出通道数需匹配负载需求。具有独立使能控制的8通道器件相比固定分频方案,可动态配置不同频率域,降低系统功耗达30%。

3. 供电电压与功耗的平衡术

在移动设备中,1.2V低电压器件的静态电流需控制在5mA以内。赛思的AC系列采用动态偏置技术,在待机模式下功耗仅3μA,同时支持1.5V至3.3V宽电压输入,适配异构计算平台的混合供电架构。

4. 封装热阻与散热设计

QFN-24封装的热阻(θJA)通常为35°C/W,当环境温度超过85°C时,需通过PCB散热过孔矩阵将结温控制在105°C以下。实测数据显示,增加4×4阵列的0.3mm散热孔可使温升降低18%。

5. 抗干扰能力的隐藏指标

电源抑制比(PSRR)>60dB@100MHz的器件能有效隔离开关电源噪声。以赛思的AC系列为例,其差分输入结构配合片上LDO,可将电源噪声引起的相位误差减少至传统方案的1/5。

以上就是关于“时钟缓冲器技术选型与设计要点”的相关内容,希望能对您有所帮助。

时钟系统

时钟系统  芯片

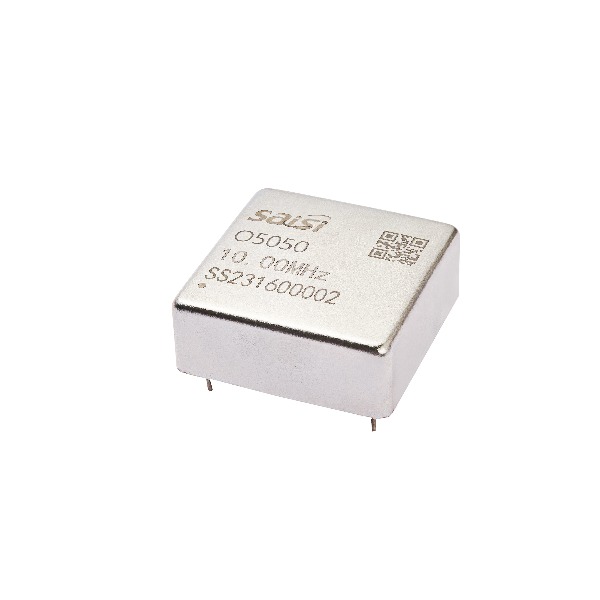

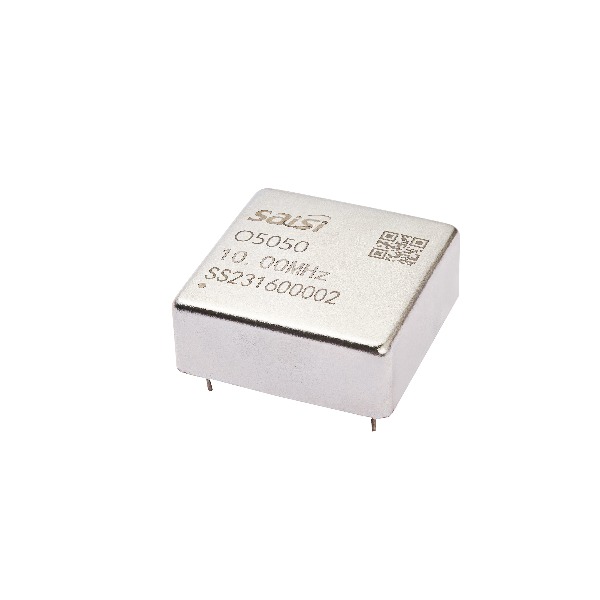

芯片  晶振&原子钟

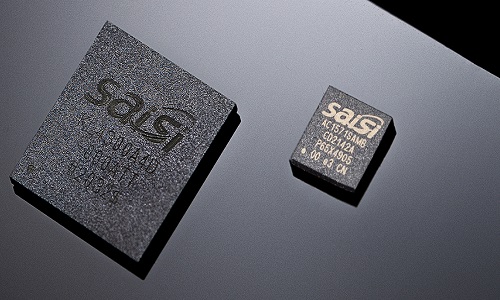

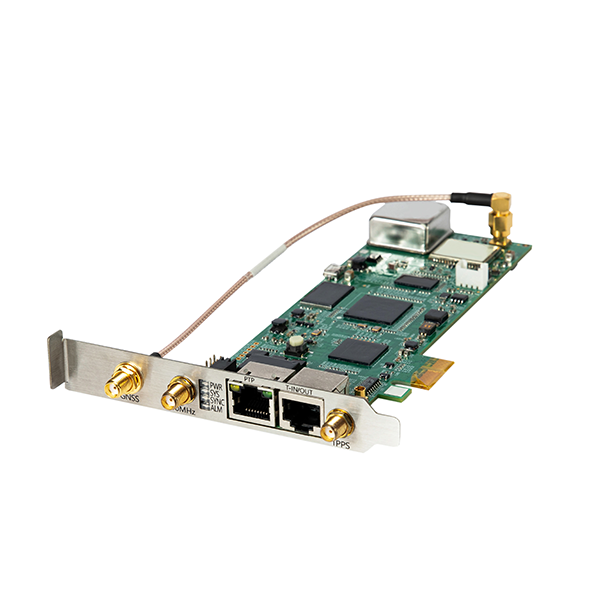

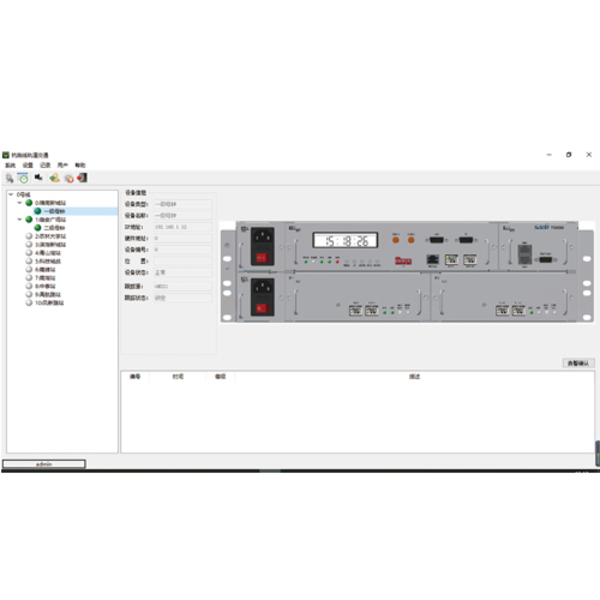

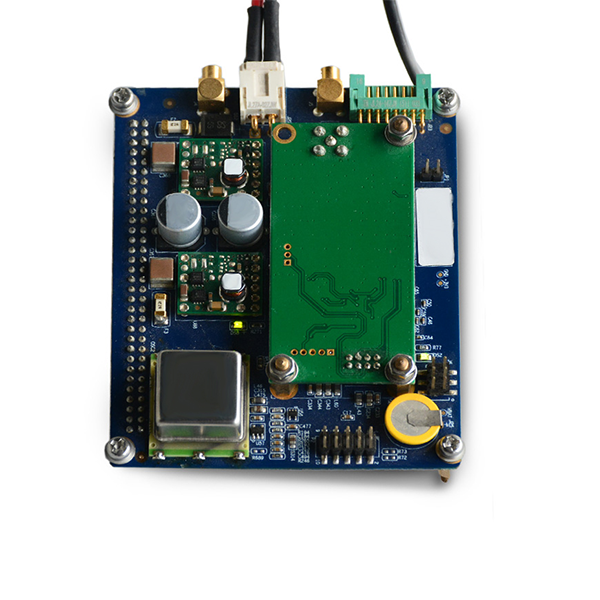

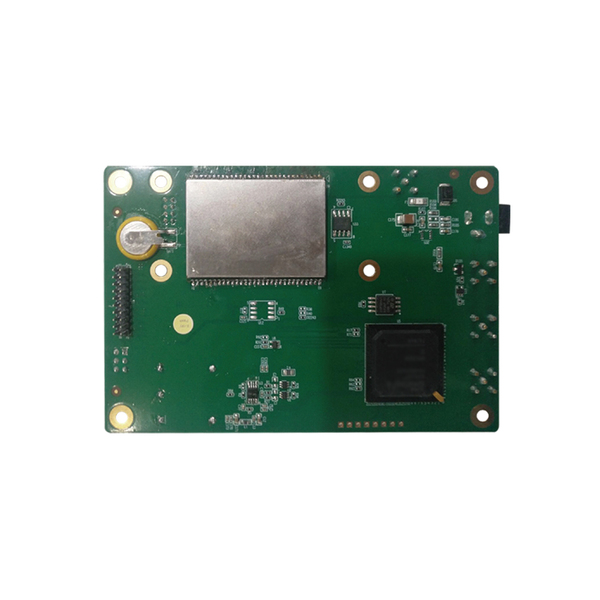

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思