在现代电子设备日益复杂的背景下,时钟发生器作为数字系统的基础组件,其性能优劣直接影响了整个系统的稳定性和效能。本文将详细介绍时钟发生器的关键技术方案,探索其在高效能、低功耗运行中的重要性及实现方式。

一、时钟发生器简介:

时钟发生器是一种关键的电子器件,其主要功能是产生稳定且精确的时钟信号。在数字电路系统中,时钟发生器确保各个组件能够同步运作,从而保证数据的准确处理和传输。无论是在计算机芯片、数字通信设备还是嵌入式系统中,时钟发生器均扮演着不可或缺的角色。

二、时钟发生器的工作原理:

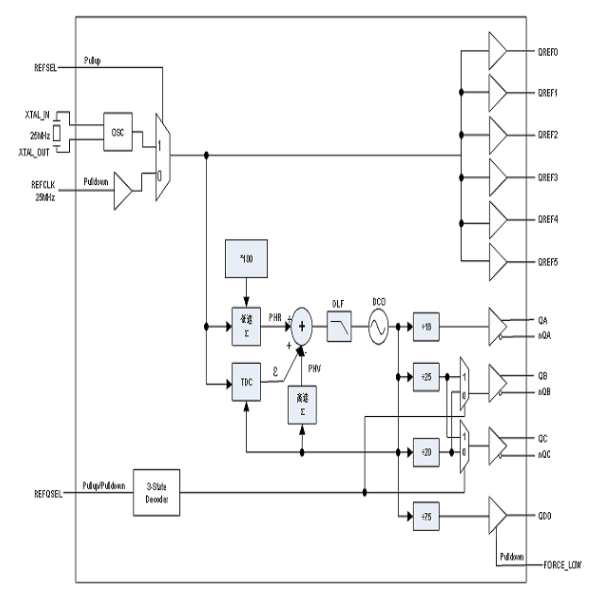

时钟发生器的核心部件是锁相环(PLL)。PLL通过比较输入时钟信号和反馈时钟信号的相位差异,动态调整输出信号的频率和相位,以实现高精度的时钟控制。这一过程确保了时钟信号的稳定性和准确性,有效避免了数据传输中的时序错误。

三、噪声与抖动的分析与抑制:

在高速串行通信中,时钟信号的噪声和抖动对系统的误码率有着直接的影响。本文提出了有效的噪声分析方法,并介绍了几种削减抖动的技术手段。例如,扩频时钟技术能够在一定程度上抑制电磁干扰,但需要进一步优化以保持信号的高稳定性和低抖动特性。

四、时钟发生器在系统应用中的关键作用:

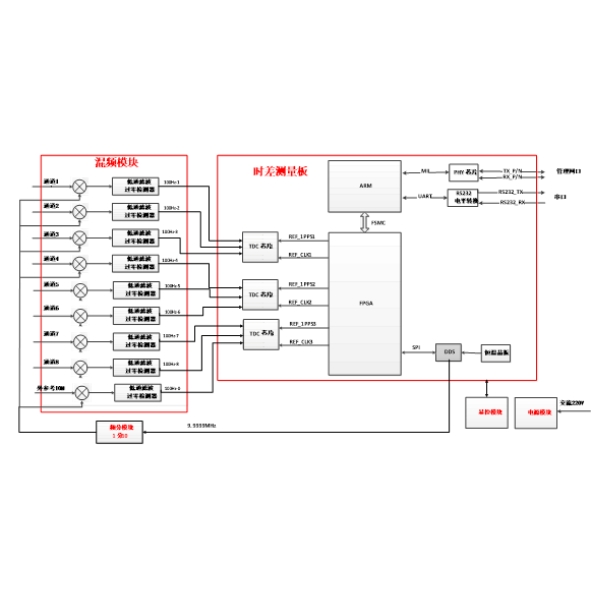

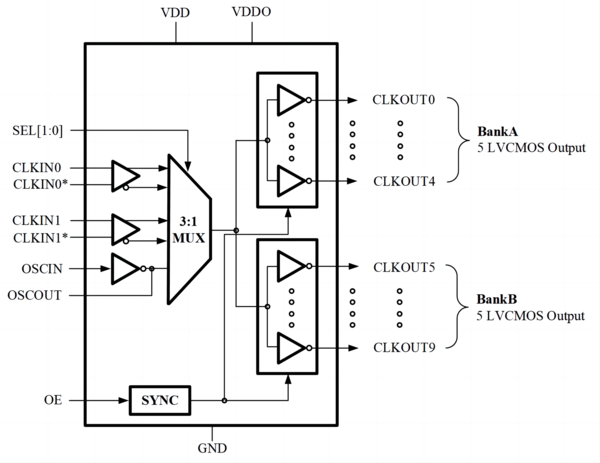

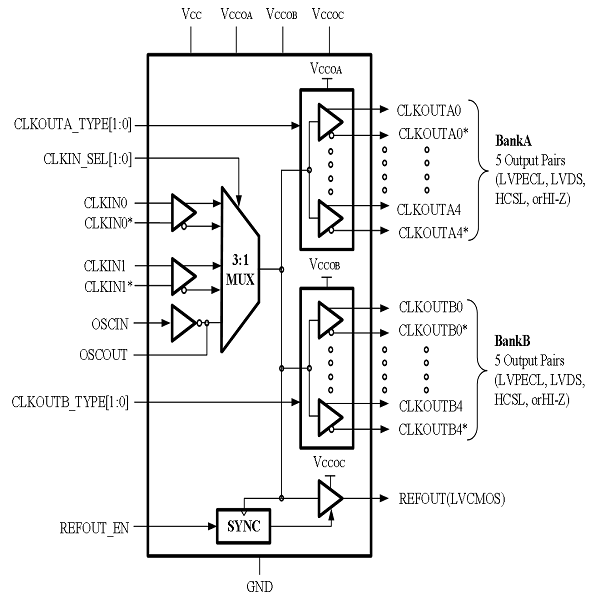

在主板启动时,时钟发生器提供符合要求的初始时钟信号,保障系统顺利启动;而在正常运行时,它则提供总线所需的各种时钟信号,协调内存芯片的工作时序。此外,高性能时钟发生器的引入还显著提高了系统的数据处理速度和能效比。

五、时钟发生器的未来发展趋势:

随着信息技术的不断进步,市场对时钟发生器频率的要求也在不断提高。未来,时钟发生器将朝着高频化、低相位噪声、宽可调范围等方向发展。研究指出,采用新材料和技术如非挥发型硅氧化氮氧化硅(SONOS)技术,可以制作出更高效的200MHz以上的时钟组件。

时钟发生器作为数字系统的核心组件,其技术的先进性和可靠性对系统整体性能至关重要。通过深入研究和技术创新,未来的时钟发生器将会更加精确、稳定,为各类电子设备提供坚实的时钟支持。

时钟系统

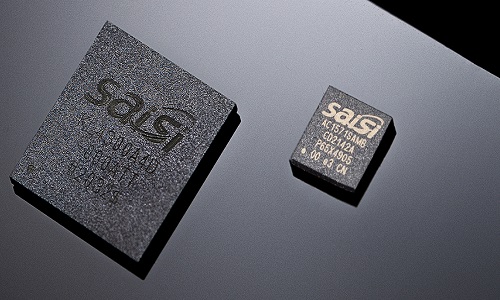

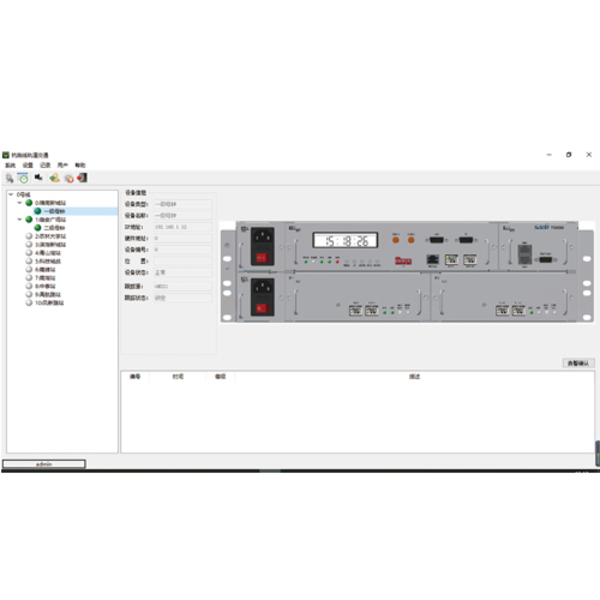

时钟系统  芯片

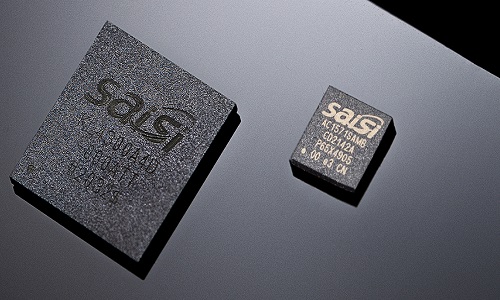

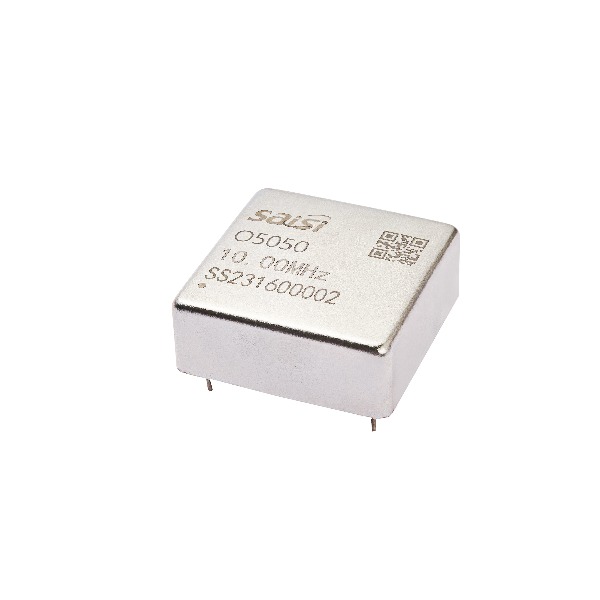

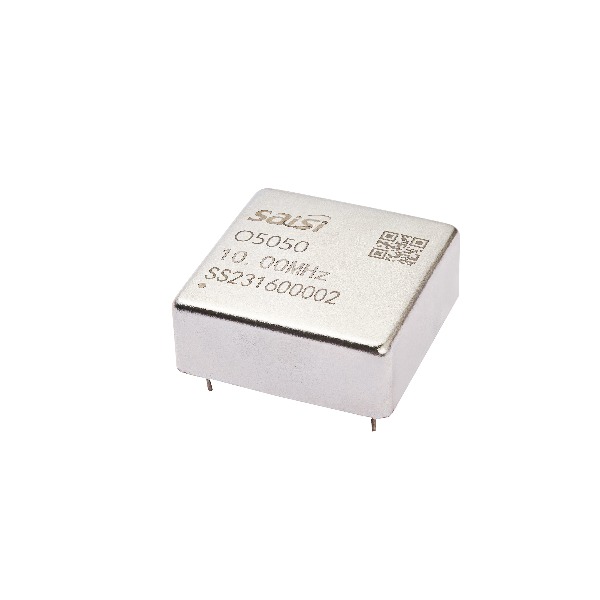

芯片  晶振&原子钟

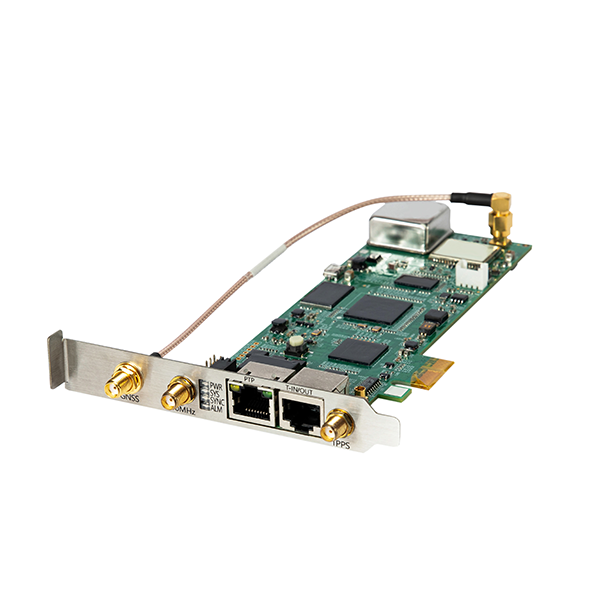

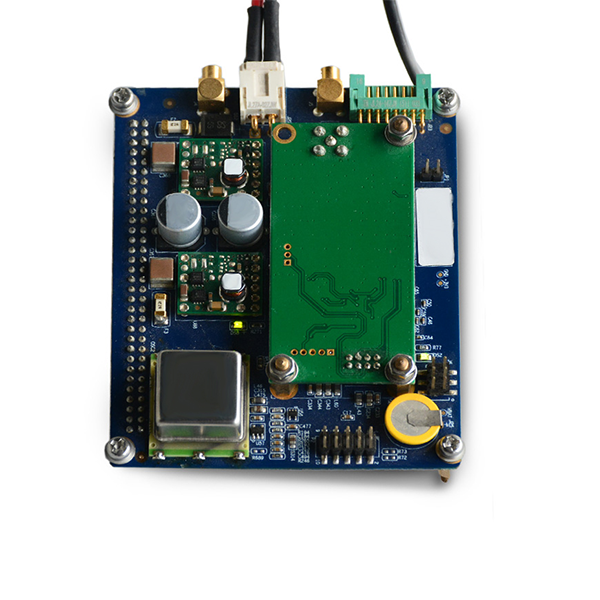

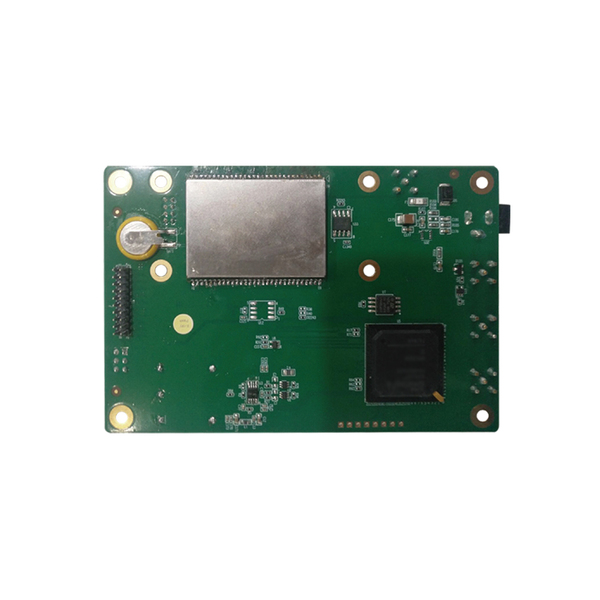

晶振&原子钟  授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

授时板卡 NTP时间同步服务器PTP时间同步服务器时间同步装置授时安全防护装置网同步设备/时频一体化设备子母钟系统BBU池时间同步时统设备钟组设备测试仪器光纤双向设备网管系统语音芯片时钟发生器时钟缓冲器时钟SOC芯片超低噪声OCXO超高稳OCXO小型化OCXO温补晶振TCXO原子钟时钟模块授时模块

智能电网

智能电网

通信网络

通信网络

智慧交通

智慧交通

智能楼宇

智能楼宇

数据中心

数据中心

前沿领域

前沿领域

新闻资讯

新闻资讯

联系我们

联系我们

人才研学中心

人才研学中心

加入赛思

加入赛思

关于赛思

关于赛思